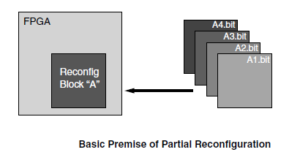

FPGA is an efficient architecture for streaming-like image processing applications. In such a category of algorithms, the application’s parallelism is expressed in instantiating a subset of hardware resources, needed to perform the desired processing, as soon as the data is acquired. However, since these resources are limited in number, the FPGA capabilities of executing larger applications is limited also. Dynamic and Partial Reconfiguration(DPR) resolves this problem by offering the possibility to reuse the FPGA resources at runtime and for a selected set of them without affecting the remaining resources being performed other computations.

This reuse might help reducing several overheads related to accelerators implementation on FPGA (i.e: Energy, Chip size …). However, the performance of a DPR-based system is affected by several critical design decisions. These decisions concern mainly the way to partition the FPGA in several execution regions as well as the application’s partitioning. Furthermore, how to perform the communication between regions and how to reduce the DPR overheads expressed in reconfiguration time should also be resolved.My Ph.D. focuses on proposing a DPR-based architecture, optimized for image processing applications while dealing with the associated, multi-dimensional and complex design space. A use case of a robust tracking algorithm called Tracking Learning Detection (TLD) is considered to explore the previously described aspects in a real context.

Another Padawan DREAM