What do we do?

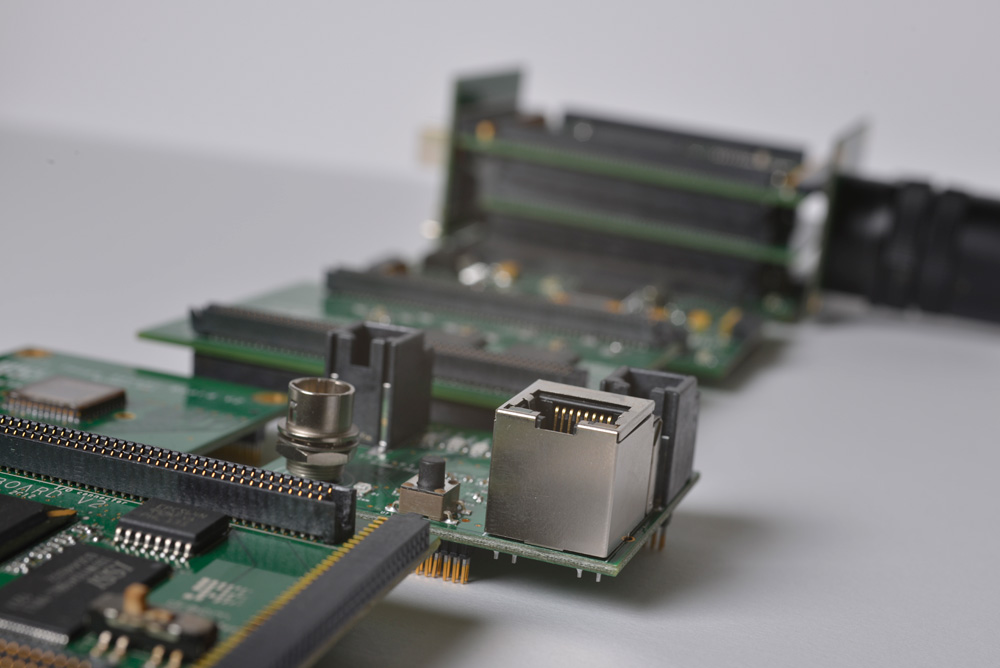

Our research concerns software and hardware sides of embedded systems, where main features are limited visibility, autonomous operation, real-time activities and constrained resources.We focuse on cutting edge research in architectural modeling and analysis, language- based approaches for embedded systems, smart cameras. Our expertise spans from design concepts to various implementation technologies for building realistic prototypes in application domains of image processing and computer vision.

LEARN MOREHaddoc: Hardware Automated Dataflow Deployment of CNNs

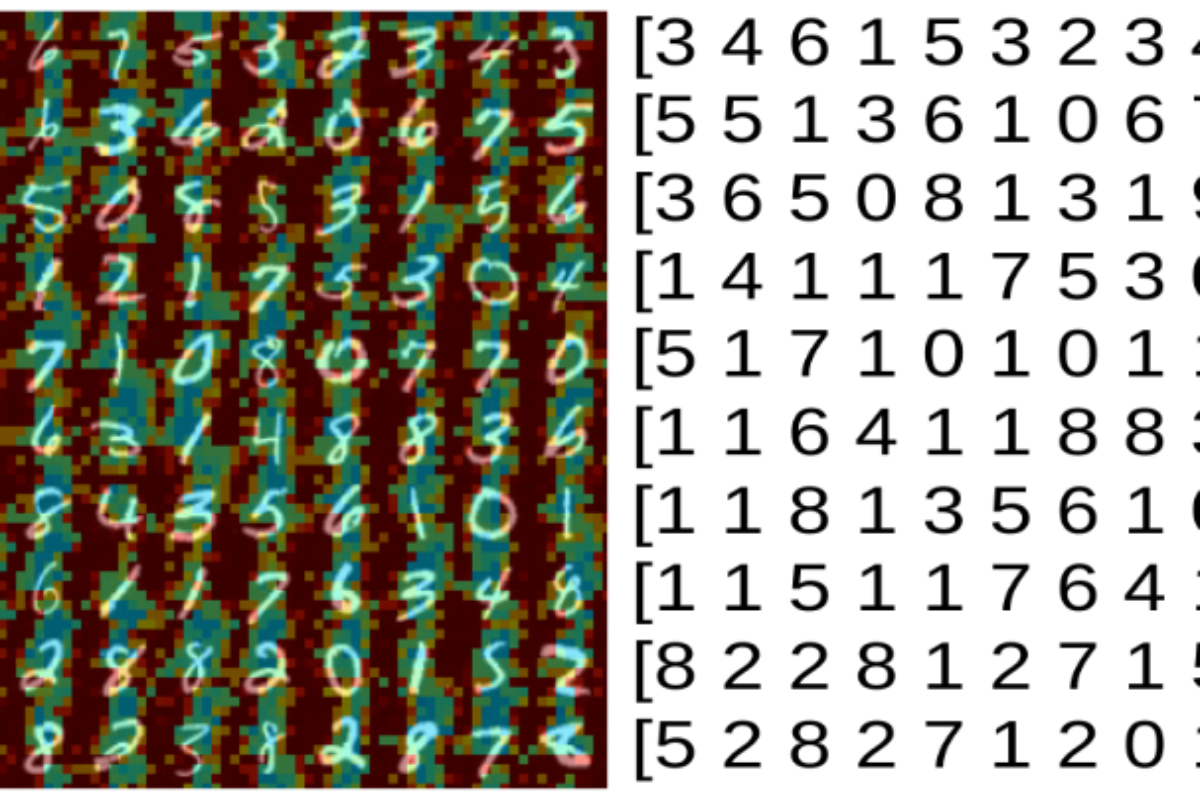

Deep Convolutional Neural Networks (CNNs) are the state of the art systems for image classification and scene understating. However, such techniques are computationally intensive and involve highly regular parallel computation. CNNs can thus benefit from a significant acceleration in execution time when running on fine grain programmable logic devices. As a consequence, several studies have proposed FPGA-based accelerators for CNNs. However, because of the huge amount of the required hardware resources, none of these studies directly was based on a direct mapping of the CNN computing elements onto the FPGA physical resources. In this work, we demonstrate the feasibility of this so-called direct hardware mapping approach and discuss several associated implementation issues. As a proof of concept, we introduce the haddoc2 open source tool, that is able to automatically transform a CNN description into a platform independent hardware description for FPGA implementation.

Download Haddoc!More details

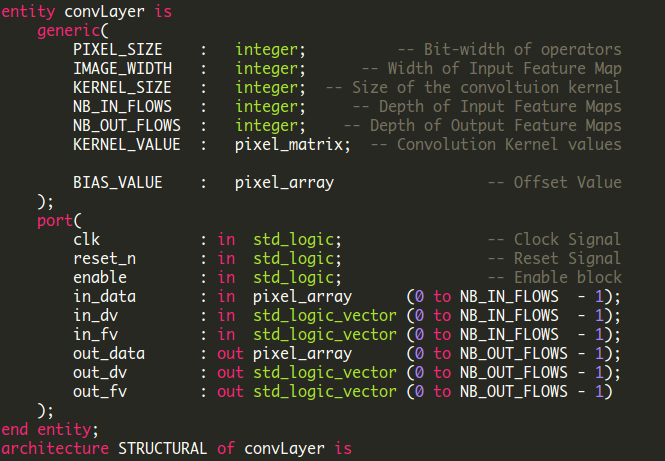

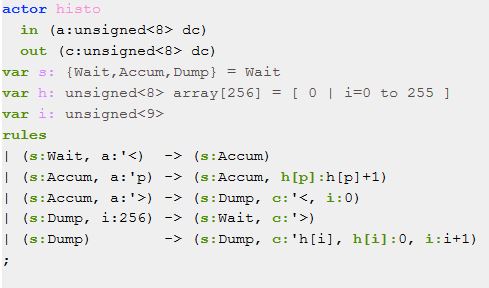

CAPH: High level dataflow programming for FPGAs

CAPH is a domain-specific language for describing and implementing stream-processing applications on reconfigurable hardware, such as FPGAs. CAPH generates VHDL code from high-level descriptions of signal or image processing applications. CAPH relies upon the actor/dataflow model of computation.CAPH is a domain-specific language for describing and implementing stream-processing applications on reconfigurable hardware, such as FPGAs. CAPH generates VHDL code from high-level descriptions of signal or image processing applications.

GET STARTED NOW

Towards stupid cameras!

Read More

CNNs. Application to FPGA-Based Smart-Cameras

Read more!

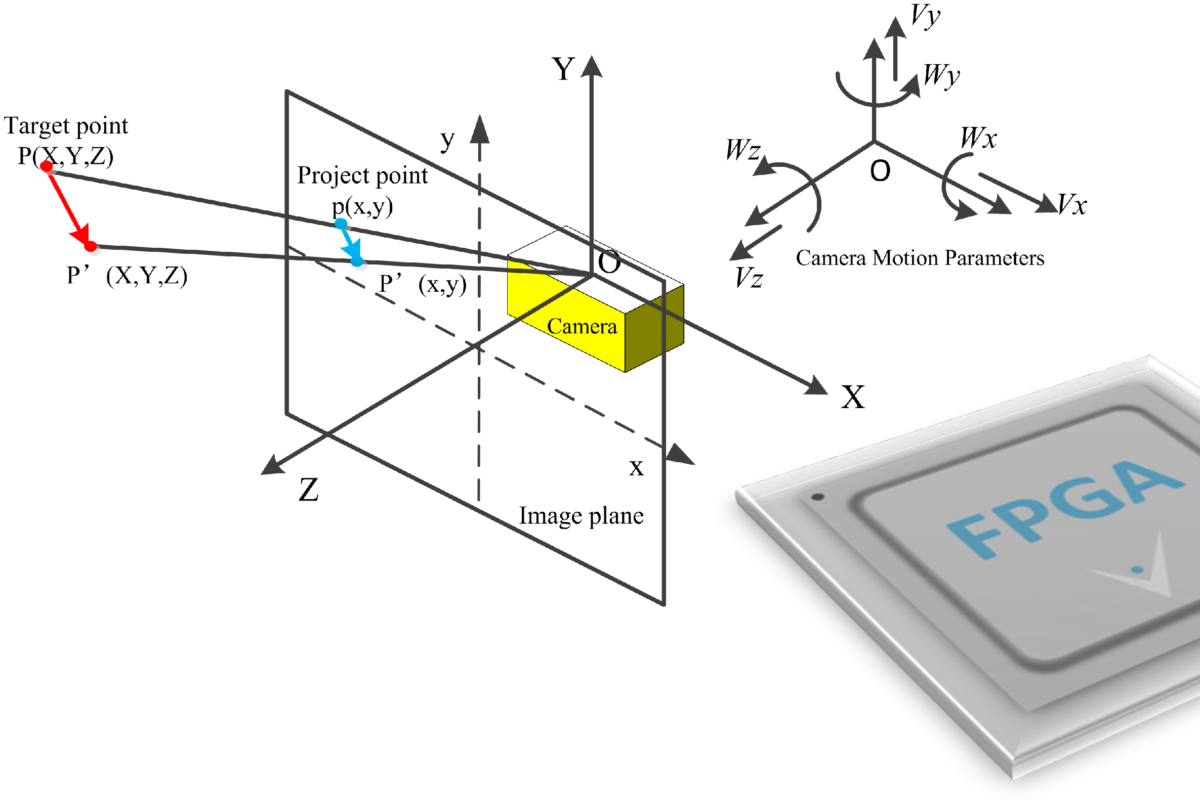

Visual Odometry Algorithm and Architecture for FPGA Acceleration

Learn More…

Dynamic and Partial Reconfiguration for Image Processing

Read More

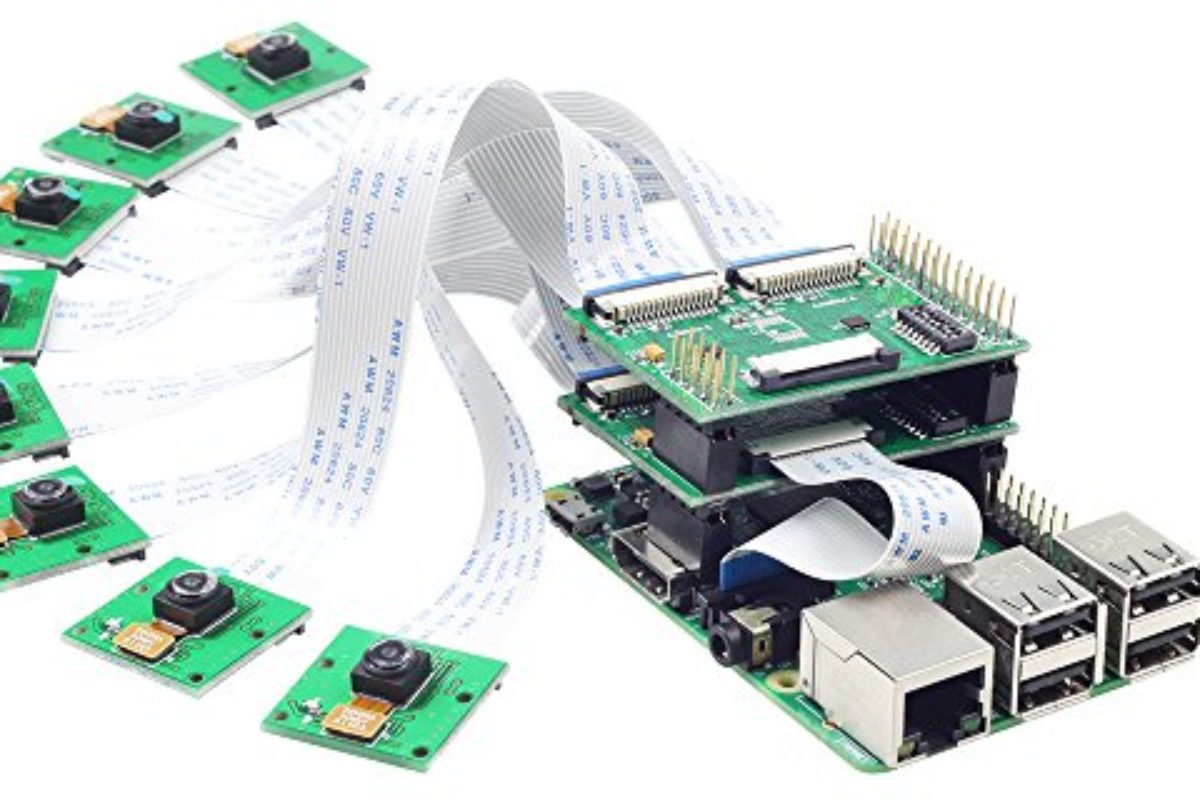

Multiview Smart Cameras

Read More